# PANCHIP Panchip Microelectronics Co., Ltd.

## PAN2416AF

## **Technology Reference Manual**

## 2.4GHz Wireless Transceiver

Version: 1.0 Release date: Sep 2017

#### Shanghai Panchip Microelectronics Co., Ltd.

Address: Room 802, No. 666 summer Shanghai Zhangjiang Hi-Tech Park Road, People's Republic of China Tel: 021-50802371 Website: <u>http://www.panchip.com</u>

#### USING THIS DOCUMENT

The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied.

#### TRADEMARKS

Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### DISCLAIMER

All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied.

#### **REVISION HISTORY**

| Version | Date     | Description | Related Documents |

|---------|----------|-------------|-------------------|

| V1.0    | Sep 2017 | Initial     | -                 |

## **Table of Contents**

| 1 | Gener  | al Description                                                    | 1  |

|---|--------|-------------------------------------------------------------------|----|

|   | 1.1    | Key Features                                                      | 1  |

|   | 1.2    | Typical Applications                                              | 2  |

| 2 | Block  | Diagram                                                           | 3  |

| 3 | PIN ir | nformation                                                        | 4  |

| - | 3.1    | Pin Assignment                                                    |    |

|   | 3.2    | Pin Descriptions                                                  |    |

|   | 3.3    | Internal Connection                                               |    |

| 4 | Electr | ical Specification                                                |    |

|   | 4.1    | Absolute Maximum Ratings                                          |    |

|   | 4.2    | Current Consumption                                               |    |

|   | 4.3    | General RF Conditions                                             |    |

|   | 4.4    | Transmitter Operation                                             | 7  |

|   | 4.5    | Receiver Operation                                                | 8  |

|   | 4.6    | DC Characteristics                                                |    |

| 5 | Opera  | tional Modes                                                      | 10 |

|   | 5.1    | Power down Mode                                                   |    |

|   | 5.2    | Standby-I Mode (STB1)                                             | 11 |

|   | 5.3    | Standby-III Mode (STB3)                                           |    |

|   | 5.4    | Standby-II Mode (STB2)                                            | 11 |

|   | 5.5    | RX Mode                                                           | 11 |

|   | 5.6    | TX Mode                                                           | 12 |

| 6 | Comn   | nunication Modes                                                  | 13 |

|   | 6.1    | Normal Mode                                                       | 14 |

|   | 6.2    | Enhanced Mode                                                     | 14 |

|   | 6.3    | Enhanced Send Mode                                                | 15 |

|   | 6.4    | Enhanced Reception Mode                                           | 15 |

|   | 6.5    | Packet Identification in Enhanced Mode                            | 16 |

|   | 6.6    | The PTX and PRX Timing of Enhanced BURST                          | 16 |

|   | 6.7    | One-To-Multi Communication at the Receiving End in Enhanced BURST | 17 |

|   | 6.8    | DATA FIFO                                                         | 18 |

|   | 6.9    | Interrupt Pin                                                     | 19 |

| 7 | SPI C  | ONTROL INTERFACE                                                  | 20 |

|   | 7.1    | SPI Instruction Format                                            | 20 |

|   | 7.2    | Timing Sequence                                                   | 22 |

| 8 | CONT   | FROL REGISTER                                                     | 24 |

| 9 | Packe  | t Format Description                                              |    |

|   | 9.1    | Packet Format for Normal BURST                                    |    |

|   | 9.2    | Packet Format for Enhanced BURST                                  |    |

# PANCHIP

|    | 9.3 Packet Format of ACK for Enhanced BURST   |    |

|----|-----------------------------------------------|----|

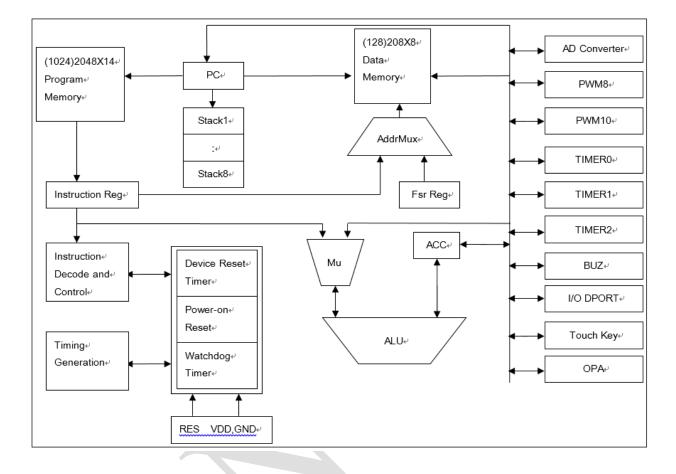

| 10 | MCU Register                                  |    |

|    | 10.1 General Description                      |    |

|    | 10.2 System Structure Diagram                 |    |

|    | 10.3 System Configuration Register            |    |

|    | 10.4 In-Circuit Serial Programming            |    |

| 11 | CPU                                           |    |

| 11 | 11.1 Internal Memory                          |    |

|    | 11.1.1 Program Internal Memory                |    |

|    | 11.1.2 Data Register                          |    |

|    | 11.2 Addressing Method                        |    |

|    | 11.2.1 Direct Addressing                      |    |

|    | 11.2.2 Immediately Addressing                 |    |

|    | 11.2.3 Indirect Addressing                    |    |

|    | 11.3 Stack                                    |    |

|    | 11.4 Working Register (ACC)                   |    |

|    | 11.4.1 Overview                               |    |

|    | 11.4.2 ACC Application                        |    |

|    | 11.5 Program Status Register (STATUS)         |    |

|    | 11.6 Prescaler (OPTION_REG)                   |    |

|    | 11.7 Program Counter (PC)                     |    |

|    | 11.8 Watchdog Counter (WDT)                   | 56 |

|    | 11.8.1 WDT Cycle                              |    |

|    | 11.8.2 Watchdog Timer Control Register WDTCON | 56 |

| 12 | System Clock                                  | 58 |

|    | 12.1 Overview                                 |    |

|    | 12.2 System Oscillator                        | 59 |

|    | 12.3 Start-up Time                            | 59 |

|    | 12.4 Oscillator Control Register              | 59 |

| 13 | Reset                                         | 61 |

|    | 13.1 Power up Reset                           |    |

|    | 13.2 Power off Reset                          |    |

|    | 13.2.1 Power off Reset Overview               |    |

|    | 13.2.2 Improving Methods of Power off Reset   | 62 |

|    | 13.3 Watchdog Reset                           |    |

| 14 | Sleep Mode                                    |    |

| 1. | 14.1 Enter Sleep Mode                         |    |

|    | 14.2 Wakeup from Sleep Mode                   |    |

|    | 14.3 Wake Up with Interrupt                   |    |

|    | 14.4 Example of Sleep Mode Application        |    |

|    | 14.5 Sleep Mode Wakeup Time                   |    |

| 15 | I/O Port                                      |    |

| 10 | 15.1 PORTA                                    |    |

|    |                                               | -  |

# PANCHIP

|    | 15.2 PORT   | ТВ                                                       | 68 |

|----|-------------|----------------------------------------------------------|----|

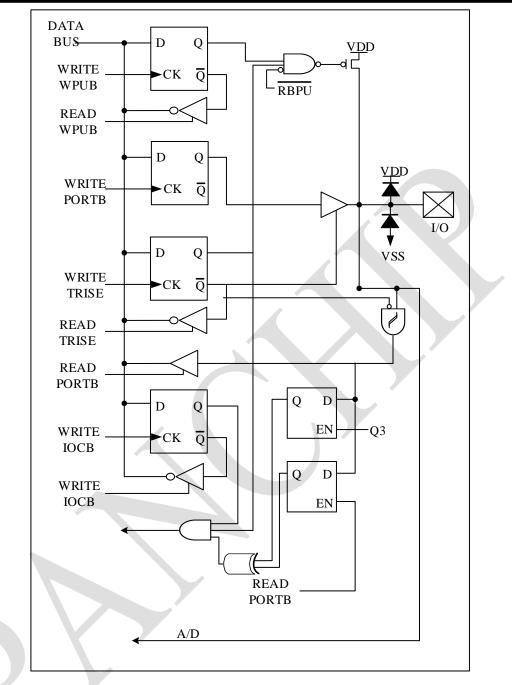

|    | 15.2.1      | PORTB Data and Control                                   | 68 |

|    | 15.2.2      | PORTB Pull Up Resistor                                   | 69 |

|    | 15.2.3      | PORTB Level Change Interrupt                             | 70 |

|    | 15.3 PORT   | ГС                                                       | 70 |

|    | 15.3.1      | PORTC Data and Control                                   | 70 |

|    | 15.3.2      | PORTC Pull Up Resistor                                   | 71 |

|    |             | ТЕ                                                       |    |

|    | 15.5 I/O    |                                                          |    |

|    | 15.5.1      | Write I/O Port                                           |    |

|    | 15.5.2      | Read I/O port                                            |    |

|    | 15.5.3      | I/O Usage Note                                           |    |

| 16 |             |                                                          |    |

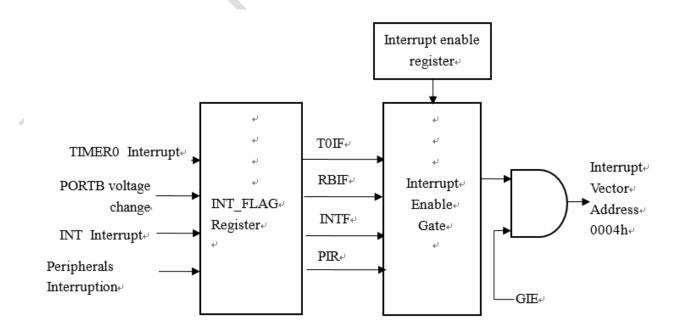

|    |             | upt Overview                                             |    |

|    | 16.2 Interr | upt Control Register                                     | 76 |

|    | 16.2.1      | Interrupt Control Register                               |    |

|    | 16.2.2      | Peripheral Interrupt Enable Register                     |    |

|    | 16.2.3      | Peripheral Interrupt Request Register                    |    |

|    |             | upt Protection Method                                    |    |

|    |             | upt Priority, and More Interrupt Nesting                 |    |

| 17 | TIMER0      |                                                          | 79 |

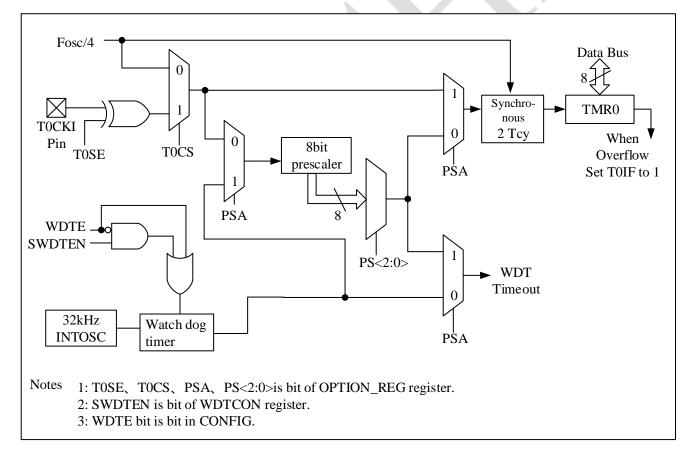

|    | 17.1 TIME   | R0 Overview                                              | 79 |

|    | 17.2 TIME   | RO Working Principle                                     | 80 |

|    | 17.2.1      | 8-Bit Timer Mode                                         |    |

|    | 17.2.2      | 8-Bit Counter Mode                                       | 80 |

|    | 17.2.3      | Software Programmer Prescaler                            | 80 |

|    | 17.2.4      | Switch the Predivider between the TIMER0 and WDT Modules |    |

|    | 17.2.5      | TIMER0 Interrupt                                         |    |

|    | 17.3 TIME   | R0 Related Register                                      | 81 |

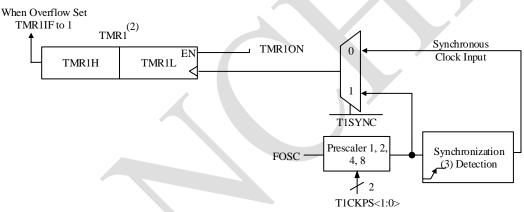

| 18 | TIMER1      |                                                          | 83 |

|    | 18.1 TIME   | ER1 Overview                                             | 83 |

|    |             | ER1 Working Principle                                    |    |

|    | 18.3 TIME   | ER1 Prescaler                                            | 83 |

|    | 18.4 TIME   | ER1 Interrupt                                            | 84 |

|    | 18.5 TIME   | ER1 Related Register                                     | 84 |

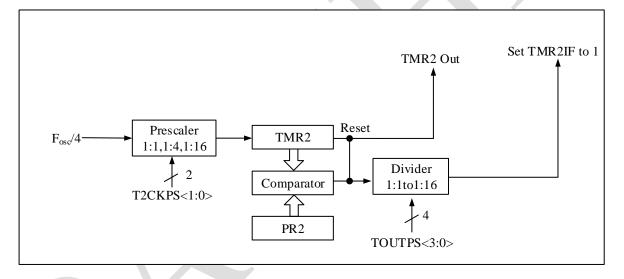

| 19 | TIMER2      |                                                          | 86 |

|    | 19.1 TIME   | ER2 Overview                                             | 86 |

|    | 19.2 TIME   | ER2 Working Principle                                    | 86 |

|    | 19.3 TIME   | ER2 Related Register                                     | 87 |

| 20 | MCU DC Ch   | aracteristics                                            | 89 |

|    | 20.1 MCU    | DC Characteristics                                       | 89 |

|    | 20.2 MCU    | AC Characteristics                                       | 89 |

|    | 20.3 Instru | ction List                                               | 90 |

|    | 20.4 Instruction Description            |  |

|----|-----------------------------------------|--|

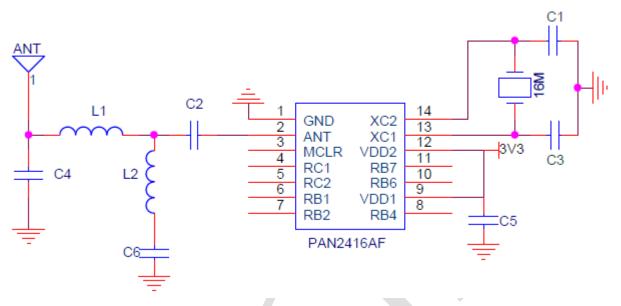

| 21 | Typical Application Circuit (Reference) |  |

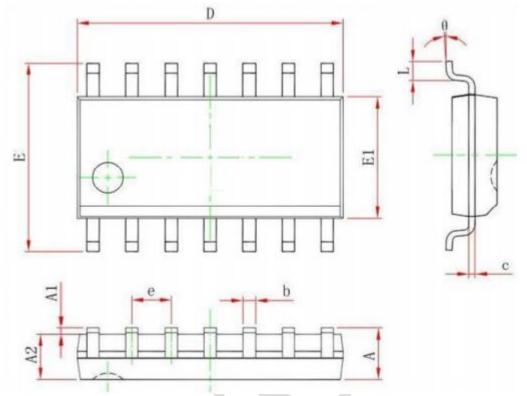

| 22 | Package Size                            |  |

| 23 | Precautions                             |  |

| 24 | Storage Conditions                      |  |

| 25 | Contact Us                              |  |

## List of Figures

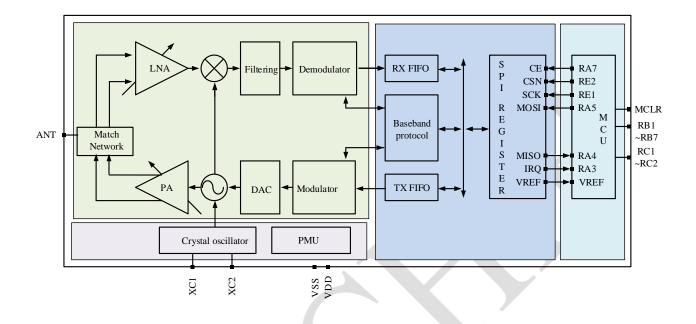

| Figure 2-1 PAN2416AF Block Diagram                                             | 3   |

|--------------------------------------------------------------------------------|-----|

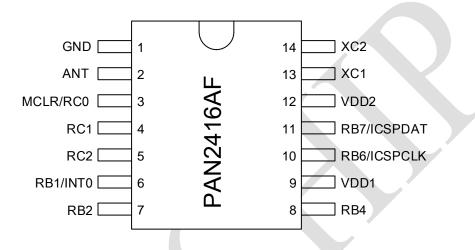

| Figure 3-1 PAN2416AF PIN Diagram                                               | 4   |

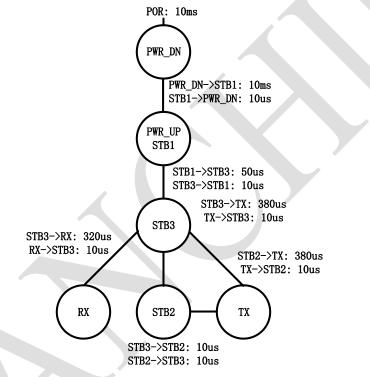

| Figure 5-1 State diagram                                                       | 10  |

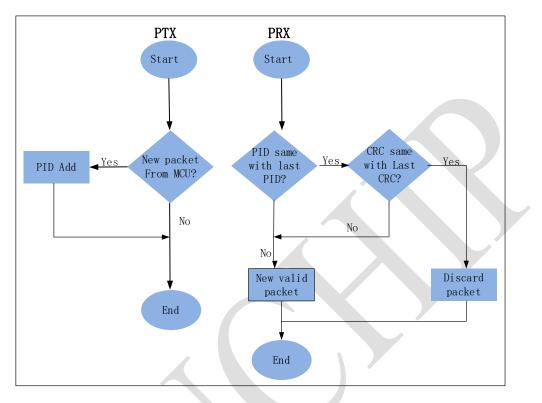

| Figure 6-1 PID generation and detection                                        | 16  |

| Figure 6-2 Timing diagram for PTX and PRX in enhanced mode (Sent successfully) | 16  |

| Figure 6-3 Multi-channel address setting                                       | 17  |

| Figure 6-4 Example of Multichannel Data Transfer Response Address              |     |

| Figure 6-5 FIFO Block Diagram                                                  | 18  |

| Figure 7-1 SPI Read Operation                                                  |     |

| Figure 7-2 SPI Write Operation                                                 | 22  |

| Figure 7-3 SPI, NOP Operation Timing Diagram                                   |     |

| Figure 10-1 System Block Diagram                                               |     |

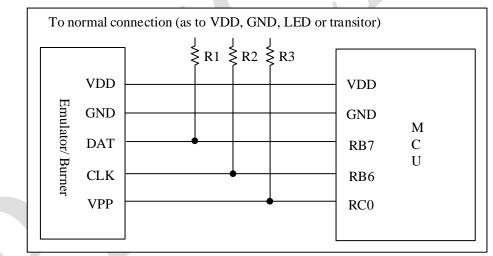

| Figure 10-2 Typical In-circuit Serial Programming Method                       | 41  |

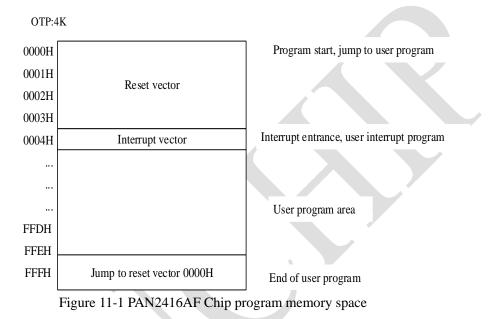

| Figure 11-1 PAN2416AF Chip program memory space                                | 42  |

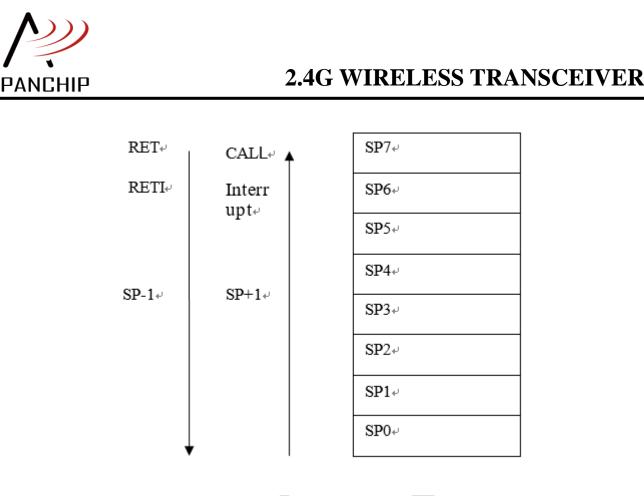

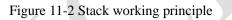

| Figure 11-2 Stack working principle                                            | 51  |

| Figure 12-1 Clock and instruction cycle timing diagram                         | 58  |

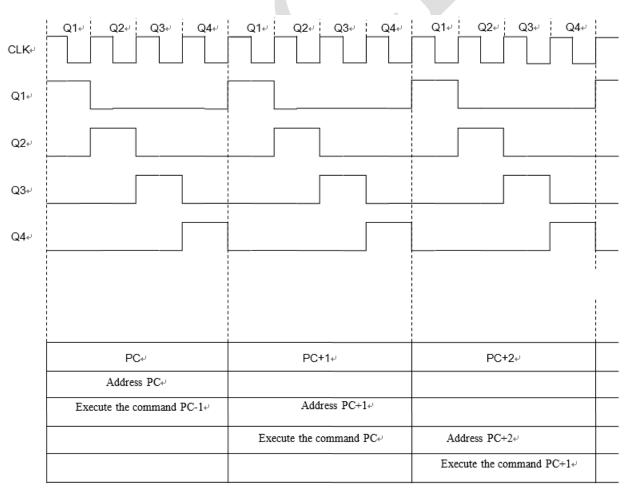

| Figure 13-1 Power off Reset Diagram                                            | 62  |

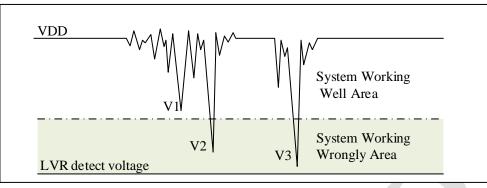

| Figure 15-1 RA/RC Block diagram                                                | 66  |

| Figure 15-2 RB Port Block Diagram                                              | 67  |

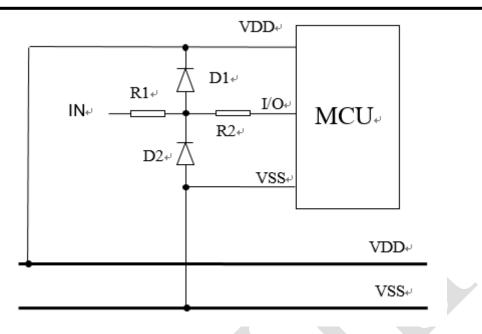

| Figure 15-3 I / O ESD protection diagram                                       | 74  |

| Figure 16-1 Interrupt execution diagram                                        | 75  |

| Figure 17-1 TIMER0/WDT Structure Diagram                                       | 79  |

| Figure 18-1 TIMER1 Block Diagram                                               | 83  |

| Figure 19-1 TIMER2 block diagram                                               | 86  |

| Figure 21-1 PAN2416AF application                                              | 109 |

| Figure 22-1 PAN2416AF package size                                             | 110 |

### **List of Tables**

| Table 3-1 PAN2416AF Pin descriptions                      | 4   |

|-----------------------------------------------------------|-----|

| Table 3-2 RF and MCU Connection Pin Description           | 5   |

| Table 4-1 Absolute Maximum Ratings                        | 6   |

| Table 4-2 Current Consumption                             |     |

| Table 4-3 General RF Conditions                           |     |

| Table 4-4 Transmitter Operation                           | 7   |

| Table 4-5 Receiver Operation                              | 8   |

| Table 4-6 DC Characteristics                              | 9   |

| Table 5-1 PAN2416AF operational modes                     |     |

| Table 6-1 Normal Mode                                     |     |

| Table 6-2 Enhanced Mode                                   | 13  |

| Table 7-1 SPI Interface                                   |     |

| Table 7-2 The Pin Description of the RF and MCU Interface | 20  |

| Table 7-3 SPI commands                                    | 20  |

| Table 7-4 SPI Operation Reference time                    | 22  |

| Table 8-1 Control Register                                | 24  |

| Table 9-1 Packet format for Normal BURST                  |     |

| Table 9-2 Packet format for Enhanced BURST                |     |

| Table 9-3 Packet format of ACK for Enhanced BURST         |     |

| Table 11-1 PAN2416AF Chip Data Memory List                | 45  |

| Table 11-2 MCU Special Function Register Summary Bank0    | 46  |

| Table 11-3 MCU Special Function Register Summary Bank1    | 48  |

| Table 11-4 MCU Special Function Register Summary Bank2    | 48  |

| Table 11-5 MCU Special Function Register Summary Bank3    | 49  |

| Table 11-6 Impact PD, TO's event table                    | 53  |

| Table 11-7 TO / PD status after reset                     | 53  |

| Table 15-1 Overall port configuration                     | 66  |

| Table 22-1 Package detail parameters for the SOP14        | 110 |

## Abbreviation

| CPU  | Central Processing Unit       |

|------|-------------------------------|

| GFSK | Gauss Frequency Shift Keying  |

| ISM  | Industrial Scientific Medical |

| LVR  | Low-Voltage Release           |

| MCU  | Microcontroller Unit          |

| OTP  | One Time Programmable         |

| RAM  | Random Access Memory          |

| RF   | Radio Frequency               |

| RTC  | Real-Time Clock               |

| SP   | Stack Pointer                 |

| SPI  | Serial Peripheral Interface   |

| WDT  | Watchdog Timer                |

|      |                               |

# **1** General Description

The PAN2416AF is a monolithic wireless transceiver chip working in the 2.400 ~ 2.483GHz world's universal ISM band. The chip integrates RF transceiver, frequency generator, crystal oscillator, modem, low-power MCU and other functional modules. Moreover, it supports one-to-multi networking and communication mode with ACK.

The user sends an instruction to the chip through the I/O port of the MCU, and the chip automatically completes the sending and receiving configuration to communicate, and automatically determines whether the data sending / receiving is successful according to the response information so as to perform resending, packet loss, resume sending and waiting, which simplifies the user program. Transmit output power, working channel and communication data rate can be configured.

The PAN2416AF requires a small number of peripheral devices to support single/double layer PCB designs.

#### **1.1 Key Features**

Featrues of the PAN2416AF include:

- MCU

- 8-bit microcontroller core

- OTP: 4K×16Bit

- Universal RAM: 176×8Bit

- Peripherals

- GPIO

- WDT

- Timer

- Including a crystal and a small amount of capacitance

- Support double or single layer PCB design, you can use the PCB microstrip antenna or wire antenna

- The chip comes with a part of the link layer communication protocol, configuration of a small amount of parameter registers, easy to be used

- RF

- Radio

- ▶ Frequency band: 2.400GHz ~ 2.483GHz

- Data rate: 2Mbps, 1Mbps, 250Kbps

- ➢ GFSK modulation

- Sleep current 2uA

- Receiver

- -83dBm@2Mbps

- ► -87dBm@1Mbps

- -91dBm@250Kbps

- Transmitter

- Output power: 8dBm

- ➢ 19mA@2dBm

- RF Synthesizer

- Fully integrated synthesizer

- Accept low cost ±60ppm 16MHz crystal for the data rate of 1Mbps and 2Mbps

- Accept low cost ±20ppm 16MHz crystal for the data rate of 250Kbps

- Protocol Engine

- Support 1 to 32 or 64 byte payload length

- Support automatic reply and automatic retransmission

- ▶ 6 data pipes receiver for 1:6 star networks

- Power Manage

- Integrated voltage regulator

- 2.2V to 3.3V supply range

- Package

- SOP14 package

- Operating Condition

- Operating temperature range: -40~85°C

#### **1.2 Typical Applications**

- wireless mouse

- Wireless gamepad

- Common remote control

- TV and set-top box remote control

- Remote control toys

- Smart home

## 2 Block Diagram

Figure 2-1 PAN2416AF Block Diagram

## **3 PIN information**

#### 3.1 Pin Assignment

PAN2416AF with SOP14 pin package pin-out is shown in Figure 3-1.

Figure 3-1 PAN2416AF PIN Diagram

#### **3.2 Pin Descriptions**

Detail pin descriptions see Table 3-2.

Table 3-1 PAN2416AF Pin descriptions

| PIN | Name    | Ю   | Function                                                                         |  |

|-----|---------|-----|----------------------------------------------------------------------------------|--|

| 1   | GND     | Р   | Ground (GND)                                                                     |  |

| 2   | ANT     | I/O | Antenna interface                                                                |  |

| 3   | RC0     | I/O | Programmable as input pin, open drain output pin                                 |  |

| 3   | MCLR    | Ι   | Write high-voltage input pin                                                     |  |

| 4   | RC1     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| 5   | RC2     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| C   | RB1     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| 6   | INT0    | 0   | External interrupt input                                                         |  |

| 7   | RB2     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| 8   | RB4     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| 9   | VDD1    | Р   | Power supply voltage input pin                                                   |  |

| 10  | RB6     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| 10  | ICSPCLK | Ι   | Programming clock pin                                                            |  |

| 11  | RB7     | I/O | Programmable as input pin, with pull-up resistor input pin, push-pull output pin |  |

| 11  | ICSPDAT | I/O | Programming data pin                                                             |  |

| 12 | VDD2 | Р | Power supply voltage input pin |

|----|------|---|--------------------------------|

| 13 | XC1  | Ι | Crystal input                  |

| 14 | XC2  | 0 | Crystal output                 |

## **3.3 Internal Connection**

| Table 3-2 RF and MCU Connection Pin Description |

|-------------------------------------------------|

|-------------------------------------------------|

| Interface function         | RF interface name of the SPI | Direction     | SPI interface name of MCU |

|----------------------------|------------------------------|---------------|---------------------------|

|                            | Kr interface name of the STT | Direction     | STT interface name of MCC |

| Mode chip select signal    | CE                           | $\rightarrow$ | RA7                       |

| SPI chip select signal     | CSN                          | →             | RE2                       |

| SPI clock signal           | SCK                          | →             | RE1                       |

| SPI Data Host out slave in | MOSI                         | $\rightarrow$ | RA5                       |

| SPI Data Host in slave out | MISO                         | ←             | RA4                       |

| Interrupt signal           | IRQ                          | ←             | RA3                       |

| The reference voltage      | VREF                         | $\rightarrow$ | VREF                      |

# **4** Electrical Specification

#### 4.1 Absolute Maximum Ratings

| Symbol           | Parameter Condition (VCC = 3V±5%, TA=25°C) | Parameter | Unit |     |    |

|------------------|--------------------------------------------|-----------|------|-----|----|

|                  |                                            | Min       | Туре | Max | 1  |

| $V_{DD}$         | Supply voltage                             | -0.3      | -    | 3.6 | V  |

| $V_I$            | Input voltage                              | -0.3      | -    | 3.6 | V  |

| $V_{O}$          | Output voltage                             | VSS       | -    | VDD | -  |

| Pd               | Total Power Dissipation (TA=-40°C~85°C)    |           | -    | 300 | mW |

| T <sub>OP</sub>  | Operating Temperature                      | -40       | -    | 85  | °C |

| T <sub>STG</sub> | Storage Temperature                        | -40       | -    | 125 | °C |

Table 4-1 Absolute Maximum Ratings

Note1: More than one or more limit maximum rating in use may cause permanent damage to the device.

Note2: Electrostatic sensitive devices follow the rules of protection when operating.

## 4.2 Current Consumption

| Table 4-2 Current Consumption |  |

|-------------------------------|--|

|-------------------------------|--|

| Symbol | Dependent Condition (VCC-2V+50/ TA-250C) | Parameter | Unit |     |     |

|--------|------------------------------------------|-----------|------|-----|-----|

| Symbol | Parameter Condition (VCC=3V±5%, TA=25°C) | Min       | Туре | Max | Umt |

|        | Sleep                                    | -         | 2    | -   | uA  |

|        | Standby I                                | -         | 30   | -   | uA  |

|        | Standby III                              | -         | 650  | -   | uA  |

|        | Standby II                               | -         | 780  | -   | uA  |

|        | TX at -35dBm output power                | -         | 9    | -   | mA  |

| ICC    | TX at -20dBm output power                | -         | 9.5  | -   | mA  |

|        | TX at 0dBm output power                  | -         | 16   | -   | mA  |

|        | TX at 2dBm output power                  | -         | 19   | -   | mA  |

|        | TX at 8dBm output power                  | -         | 30   | -   | mA  |

|        | TX at 13dBm output power                 | -         | 66   | -   | mA  |

|        | RX at 2Mbps                              | -         | 16.5 | -   | mA  |

| RX at 1Mbps   | - | 15.5 | - | mA |

|---------------|---|------|---|----|

| RX at 250kbps | - | 15   | - | mA |

#### 4.3 General RF Conditions

| Chl                 |                                            | Parame | <b>T</b> T •4 |      |      |

|---------------------|--------------------------------------------|--------|---------------|------|------|

| Symbol              | Parameter Condition (VCC = 3V±5%, TA=25°C) | Min    | Туре          | Max  | Unit |

| $f_{OP}$            | Operating frequency                        | 2400   |               | 2483 | MHz  |

| PLL <sub>res</sub>  | PLL Programming resolution                 | -      | 1             | -    | MHz  |

| $f_{\textit{XTAL}}$ | Crystal frequency                          | -      | 16            | -    | MHz  |

| DR                  | Data rate                                  | 0.25   | -             | 2    | Mbps |

| $\Delta f_{250K}$   | Frequency deviation at 250kbps             |        | 125           | 150  | KHz  |

| $\Delta f_{1M}$     | Frequency deviation at 1Mbps               |        | 160           | 300  | KHz  |

| $\Delta f_{2M}$     | Frequency deviation at 2Mbps               |        | 320           | 550  | KHz  |

| $FCH_{250K}$        | Channel spacing at 250Kbps                 |        | 1             | -    | MHz  |

| FCH <sub>1M</sub>   | Channel spacing at 1Mbps                   | -      | 1             | -    | MHz  |

| FCH <sub>2M</sub>   | Channel spacing at 2Mbps                   | -      | 2             | -    | MHz  |

#### Table 4-3 General RF Conditions

## 4.4 Transmitter Operation

| Group al | Demonster Can dition (VCC 2V/ 50/ TA-250C)      | Parameter | TT   |     |      |

|----------|-------------------------------------------------|-----------|------|-----|------|

| Symbol   | Parameter Condition (VCC = 3V±5%, TA=25°C)      | Min       | Туре | Max | Unit |

| PRF      | Typical output power                            | 2         | 8    | 8   | dBm  |

| PRFC     | Output Power Range                              | -35       | -    | 8   | dBm  |

| PBW1     | 20dB Bandwidth for Modulated Carrier at 250Kbps | -         | 500  | -   | KHz  |

| PBW2     | 20dB Bandwidth for Modulated Carrier at 1Mbps   | -         | 1    | -   | MHz  |

| PBW3     | 20dB Bandwidth for Modulated Carrier at 2Mbps   | -         | 2    | -   | MHz  |

## 4.5 Receiver Operation

| C 1                                                       |                                            | Param | TT   |     |      |

|-----------------------------------------------------------|--------------------------------------------|-------|------|-----|------|

| Symbol                                                    | Parameter Condition (VCC = 3V±5%, TA=25°C) |       | Туре | Max | Unit |

| $RX_{max}$ Maximum received signal at <0.1% BER           |                                            | -     | 0    |     | dBm  |

| RXSENS3                                                   | Sensitivity (0.1%BER) @250Kbps             |       | -91  | -   | dBm  |

| RXSENS2                                                   | Sensitivity (0.1%BER) @1Mbps               | -     | -87  |     | dBm  |

| RXSENS1                                                   | Sensitivity (0.1%BER) @2Mbps               | -     | -83  | -   | dBm  |

| C/I <sub>co</sub>                                         | C/I Co-channel (@250Kbps)                  | -     | 2    | -   | dBc  |

| $C/I_{1ST}$                                               | 1st Adjacent Channel Selectivity C/I       | -     | -8   | -   | dBc  |

| $C/\mathrm{I}_{2ND}$                                      | 2nd Adjacent Channel Selectivity C/I       | -     | -18  | -   | dBc  |

| $C/I_{3RD}$                                               | 3rd Adjacent Channel Selectivity C/I       | -     | -24  | -   | dBc  |

| $C / I_{4TH}$ 4th Adjacent Channel Selectivity C/I        |                                            | -     | -28  | -   | dBc  |

| $C / I_{5TH}$ 5th Adjacent Channel Selectivity C/I        |                                            | -     | -32  | -   | dBc  |

| $C/\mathrm{I}_{_{6TH}}$                                   | 6th Adjacent Channel Selectivity C/I       |       | -35  | -   | dBc  |

| C/I <sub>co</sub>                                         | C/I Co-channel (@1Mbps)                    |       | 10   | -   | dBc  |

| $C/I_{1ST}$                                               | 1st Adjacent Channel Selectivity C/I       | -     | 1    | -   | dBc  |

| $C/I_{2ND}$                                               | 2nd Adjacent Channel Selectivity C/I       | -     | -18  | -   | dBc  |

| $C/\mathrm{I}_{_{3RD}}$                                   | 3rd Adjacent Channel Selectivity C/I       | -     | -23  | -   | dBc  |

| $C / I_{4TH}$ 4th Adjacent Channel Selectivity C/I        |                                            | -     | -28  | -   | dBc  |

| C / I <sub>5TH</sub> 5th Adjacent Channel Selectivity C/I |                                            | -     | -32  | -   | dBc  |

| $C/\mathrm{I}_{6TH}$                                      | 6th Adjacent Channel Selectivity C/I       |       | -35  | -   | dBc  |

| C/I <sub>co</sub>                                         | C/I Co-channel (@2Mbps)                    | -     | 10   | -   | dBc  |

Table 4-5 Receiver Operation

| $C/I_{1ST}$ | 1st Adjacent Channel Selectivity C/I | - | -6  | - | dBc |

|-------------|--------------------------------------|---|-----|---|-----|

| $C/I_{2ND}$ | 2nd Adjacent Channel Selectivity C/I | - | -10 | - | dBc |

| $C/I_{3RD}$ | 3rd Adjacent Channel Selectivity C/I | - | -22 | - | dBc |

| $C/I_{4TH}$ | 4th Adjacent Channel Selectivity C/I | - | -28 | - | dBc |

| $C/I_{5TH}$ | 5th Adjacent Channel Selectivity C/I | - | -34 |   | dBc |

Note1: In the crystal 16MHz integer multiples (such as 2416, 2432MHz, etc) channels and the adjacent positive and negative 1MHz channels, receiving sensitivity degenerate 2dB.

Note2: The maximum length of data sent in 250kbps mode is 16 bytes.

### **4.6 DC Characteristics**

| Growbal         | Demonster Condition (VCC 2V) 50( TA-250C)  | Paramet | T.I  |         |      |

|-----------------|--------------------------------------------|---------|------|---------|------|

| Symbol          | Parameter Condition (VCC = 3V±5%, TA=25°C) | Min     | Туре | Max     | Unit |

| VDD             | Supply voltage                             | 2.2     | 3    | 3.3     | V    |

| VSS             | Ground                                     | -       | 0    | -       | V    |

| V <sub>OH</sub> | Output high level voltage                  | VDD-    | -    | VDD     | V    |

| V OH            |                                            | 0.3     |      |         |      |

| $V_{OL}$        | Output low level voltage                   | VSS     | -    | VSS+0.3 | V    |

| • OL            |                                            |         |      |         |      |

| $V_{IH}$        | Input high level voltage                   | VDD-    | -    | VDD     | V    |

| V <sub>IH</sub> |                                            | 0.3     |      |         |      |

| V               | Input low level voltage                    | VSS     | -    | VSS+0.3 | V    |

| V <sub>IL</sub> |                                            |         |      |         |      |

#### Table 4-6 DC Characteristics

# **5** Operational Modes

This chapter describes the various operating modes of the PAN2416AF and the methods for controlling the chip to get into each operating mode. PAN2416AF chip comes with the state machine controlled by the chip's internal register configuration values and external pin signals.

Figure 5-1 is PAN2416AF's working state diagram, showing the transition between five operating modes. PAN2416AF begins to work properly when VDD is greater than 2.2V. Even entering sleep mode, the MCU can still send configuration commands through the SPI and the CE pin to make the chip get into the other five states.

Figure 5-1 State diagram

The Table 5-1 describes how to configure the operational modes and the functions.

Table 5-1 PAN2416AF operational modes

| MODE        |                           | PWR_DN | STB1 | STB3 | STB2          | RX           | ТХ               |

|-------------|---------------------------|--------|------|------|---------------|--------------|------------------|

|             | PWR_UP                    | 0      | 1    | 1    | 1             | 1            | 1                |

|             | EN_PM                     | 0      | 0    | 1    | 1             | 1            | 1                |

| CONTROL BIT | CE                        | 0      | 0    | 0    | 1             | 1            | 1                |

|             | PRIM_RX                   | Х      | Х    | Х    | 0             | 1            | 0                |

|             | FIFO state                | Х      | Х    | Х    | TX FIFO empty | Х            | Data in TX FIFOs |

|             | SPI operation             |        |      |      | $\checkmark$  | $\checkmark$ | $\checkmark$     |

| FUNCTION    | Keep register value       |        |      |      | $\checkmark$  | $\checkmark$ | $\checkmark$     |

| DESCRIPTION | Crystal oscillator work   | Х      |      |      | $\checkmark$  | $\checkmark$ | $\checkmark$     |

|             | Crystal oscillator output | Х      | Х    | Х    | $\checkmark$  | $\checkmark$ | $\checkmark$     |

| Main power manage-   | Х | Х |   |   |   | $\checkmark$ |

|----------------------|---|---|---|---|---|--------------|

| ment work            |   |   |   |   |   |              |

| Transmit module ena- | Х | Х | Х | Х | Х |              |

| bled                 |   |   |   |   |   |              |

| Receive module ena-  | Х | Х | Х | Х |   | Х            |

| bled                 |   |   |   |   |   |              |

#### 5.1 Power down Mode

In sleep mode, all functions of the PAN2416AF are turned off, keeping the current consumption to a minimum. After entering sleep mode, PAN2416AF stops working, but the register's contents remain unchanged. Sleep mode is controlled by the PWR\_UP bit in the register.

#### 5.2 Standby-I Mode (STB1)

In standby mode-I, the chip maintains crystal oscillation but doesn't output to other modules, the remaining functional modules are off, the current consumption is small. In sleep mode, the chip enters standby mode -I by setting the register PWR\_UP to 1. In transmit or receive mode, the chip returns to standby mode -I by setting the CE and EN\_PM control signals to 0.

#### 5.3 Standby-III Mode (STB3)

In standby mode -I, the chip enters standby mode -III when the EN\_PM control signal is set to 1. The main purpose of the standby mode -III is to make the power management module of the chip prior to the output of the oscillator.

#### 5.4 Standby-II Mode (STB2)

Transmitting terminal TX FIFO register is empty and the CE pin is set to 0, entering standby mode-II (standby mode-II can usually be understood as the preparatory transmission mode). At this point, the crystal oscillator has a strong output drive capability and chip's power management module is turned on.In standby mode-II, if there are data packets into the TX FIFO, the chip's internal phase-locked loop immediately start to work and the transmitter will launch the packet after a period of phase-locked loop.

#### 5.5 RX Mode

When PWR\_UP, PRIM-RX, EN\_PM, CE are set to 1, the chip enters receiving mode.

In the RX mode, the RF part receives the signal from the antenna, and then amplifies, down-converts, filters and demodulates the received signal. According to the address, check code, data length, etc., to determine whether the package is effective. If it is, then the effective package will be uploaded to RX FIFO, and the RF part will report interruption. If the RX FIFO is full, the received data packets will be discarded.

#### 5.6 TX Mode

When PWR\_UP, EN\_PM is set, PRIM-RX is set to 0, CE is set and valid data exists in the TX FIFO, the chip enters to transmit mode. The PAN2416AF is kept in the transmit mode before the data packet is sent. After sending, the chip returns to standby mode. The PAN2416AF uses PLL open loop transmit mode, and the data packet is sent by single packet.

## **6** Communication Modes

The PAN2416AF completes the communication function together with the MCU. The link layer, such as data framing, parity check, address judgment, scrambling data blanking, data retransmission and ACK response, is done internally by the chip without MCU involvement.

The PAN2416AF chip can be configured as two different RX FIFO registers (32 bytes) or one RX FIFO register (64 bytes, six receive channels are shared), two different TX FIFO registers (32 bytes), or one TX FIFO register (64 bytes). The MCU can access the FIFO registers in Sleep and Standby modes.

PAN2416AF chip mainly has two kinds of data communication modes:

- 1) Communication mode without automatic retransmission without ACK (hereinafter referred to as normal mode). The transmitter can use the command W\_TX\_PAYLOAD, REUSE\_TX\_PL and so on.

- 2) Communication mode with automatic retransmission with ACK (latter referred to as enhanced mode). The transmitter can use the command W\_TX\_PAYLOAD, W\_TX\_PAYLOAD\_NO-ACK, REUSE\_TX\_PL, etc. The receiver can use the command W\_ACK\_PAYLOAD, etc.

| Name of the communication            | Normal mode                              |                   |  |  |

|--------------------------------------|------------------------------------------|-------------------|--|--|

| Communication party                  | PTX                                      | PRX               |  |  |

| Characteristic                       | One-way transmission                     | One-way receiving |  |  |

| Frame mode of sending data           | I                                        | -                 |  |  |

| Command for openning the REUSE_TX_PL | Repeatedly send the previous packet data | -                 |  |  |

| Table 6-1 Normal | Mode |

|------------------|------|

|------------------|------|

| Table 6-2 Enhanced Mode |

|-------------------------|

|-------------------------|

| Name of the communication        | Enhanced mode                |                                    |

|----------------------------------|------------------------------|------------------------------------|

| Communication party              | PTX                          | PRX                                |

| Characteristic                   | After sending data, wait to  | After receiving the data, send the |

|                                  | receive ACK                  | ACK back                           |

| Frame mode of sending data       | Send data framing mode II    | Send ACK framing mode III back     |

| PTX uses the REUSE_TX_PL command | Repeatedly send the previ-   | Send ACK back every time a packet  |

|                                  | ous packet data              | is received                        |

| PTX uses the W_TX_PAYLOAD com-   | After sending data, wait to  | After receiving the data, send ACK |

| mand                             | receive ACK PAYLOAD          | PAYLOAD back, framing mode II      |

| PRX uses the W_ACK_PAYLOAD com-  |                              |                                    |

| mand                             |                              |                                    |

| PTX uses the W_TX_PAYLOAD_NO     | Send a data, not waiting for | Receive data, not sending ACK back |

| ACK command                      | ACK, framing mode II         |                                    |

#### 6.1 Normal Mode

In normal mode, the transmitter fetches data from the TX FIFO register and sends it. After the transmission is complete, the interrupt is reported (the interrupt needs to be cleared) and the TX FIFO register clears the data (TX FIFO needs to be cleared). When the receiver receives a valid address and data, it reports the interrupt to the MCU. The MCU can then read the data from the RX FIFO register (the TX FIFO and RX FIFO need to be cleared and the interrupt needs to be cleared).

Normal mode, (0X01) EN\_AA register is set to 0X00, (0X04) SETUP\_RETR register is set to 0X00, (0X1C) DYNPD register is set to 0X00, the low 3 bit of the (0X1D) FEATURE register is set to 000.

#### 6.2 Enhanced Mode

In enhanced mode, the party initiating the communication is referred to as the PTX (primary originator), and the party receiving the data and responding there to is referred to as PRX (primary terminator). After the PTX sends the data, the chip waits for the response signal. After the PRX receives the valid data, it replies with the response signal. If PTX did not receive the response signal within the specified time, it will automatically resend the data. Automatic retransmission and autoanswer function come with the PAN2416AF chip, without MCU's involvement.

PTX automatically switches to receive mode and waits for a reply after sending data. If the correct answer signal is not received within the specified time, the PTX will resend the same data packet until it receives a reply signal or if the number of transfers exceeds the value of ARC (SETUP\_RETR register), a MAX\_RT interrupt is generated. The PTX receives the response signal, which means the data has been transmitted successfully (PRX received valid data), cleared the data in TX FIFO and generated TX\_DS interrupt (TX FIFO and RX FIFO need to be cleared and interrupt needs to be cleared).

PRX will send an ACK signal back every time a packet of valid data is received. If the data is new (the PID value is different from the previous packet data), it will be saved to RX FIFO, or it will be discarded.

Enhanced mode, we need to ensure that the PTX TX address (TX\_ADDR), Channel 0 RX address (such as RX\_ADDR\_P0), and PRX RX address (such as RX\_ADDR\_P5) keep the same. For example: In Figure 5, PTX5 corresponds to PRX data channel 5, the address is set as follows:

PTX5: TX\_ADDR=0xC2C3C4C5C1

PTX5: RX\_ADDR\_P0=0xC2C3C4C5C1

RX: RX\_ADDR\_P5=0xC2C3C4C5C1

The enhanced mode has the following characteristics:

- 1) Reduce MCU control and simplify software operation.

- 2) Strong anti-interference ability, reduce packet loss due to instantaneous co-channel interference in wireless transmission and easy to develop frequency hopping algorithm.

- 3) During the re-transmission, reduce the operation time of the data written and being sent every

time the MCU passes through the SPI interface.

#### 6.3 Enhanced Send Mode

- 1) When CE is set to 0, the PRIM\_RX bit in the CONFIG register is set to 0.

- 2) When the data is sent, the sending address (TX\_ADDR) and the valid data (TX\_PLD) are written to the address register and the TX FIFO by the SPI interface by the byte. When CSN pin is low, the data is written. When the CSN pin is high again, the data completes being written.

- 3) When CE changes from 0 to 1, the transmission is started (CE at least continues to set 1 above 30us, the operation takes effect).

- 4) In auto answer mode (SETUP\_RETR register is not set to 0, ENAA\_P0 = 1), PTX will automatically switch channel 0 to receive mode and wait for response signal immediately after sending data. If an ACK signal is received within the valid response time, the data transmission is considered as successful and the TX\_DS bit in the status register is set and the data in the TX FIFO is automatically cleared. If no response signal is received within the set time range, the data is automatically retransmitted.

- 5) If the automatic transfer counter (ARC\_CNT) overflows (exceeds the set value), the MAX\_RT bit in the status register is set to 1 and data in the TX FIFO is not cleared. When MAX\_RT or TX\_DS is 1, the IRQ pin generates a low-level interrupt (interrupts must be enabled). Interrupts can be reset by writing to the status register.

- 6) The packet loss counter (PLOS\_CNT) is incremented by one each time a MAX\_RT interrupt is generated. Automatic transmission counter ARC\_CNT count the times of the retransmission data packets. Packet Loss Counter PLOS\_CNT counts the number of packets that still fail to be transmitted when the maximum number of transmission is allowed.

- 7) After the MAX\_RT or TX\_DS interrupt is generated, the system enters standby mode.

#### 6.4 Enhanced Reception Mode

- 1) When CE is set to 0, the PRIM\_RX bit in the CONFIG register is set to 1. The channel ready to receive data must be enabled (EN\_RXADDR register) and all auto-acknowledge functions for the data channel operating in enhanced communication mode are enabled by the EN\_AA register, and the valid data width is set by the RX\_PW\_PX register.

- 2) The receive mode is started by setting CE to 1.

- 3) After the preset waiting time, PRX starts to detect the wireless signal.

- 4) After receiving a valid data packet, the data is stored in RX\_FIFO and the RX\_DR bit is set to 1, an interrupt is generated. The RX\_P\_NO bit in the status register shows which channel the data was received from.

- 5) Send an ACK response signal automatically.

- 6) If CE remains 1, continue to receive mode. If CE is set to 0, enter standby mode-III.

- 7) The MCU reads the data through the SPI port at the proper rate.

#### 6.5 Packet Identification in Enhanced Mode

Figure 6-1 PID generation and detection

Each packet of data includes a two-bit PID (packet flag), to help the receiver to identify the data is new or retransmitted to prevent the multiple data packets into the same store, PID generation and detection is shown in Figure 6-1. The PID value adds one once the transmitting terminal gets a new packet from the MCU.

#### 6.6 The PTX and PRX Timing of Enhanced BURST

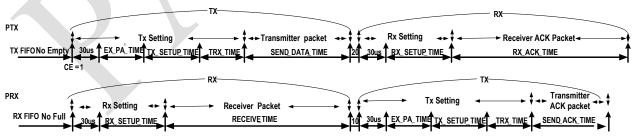

Figure 6-2 Timing diagram for PTX and PRX in enhanced mode (Sent successfully)

Figure 6-2 shows a chip internal timing diagram of a PTX and PRX communication, to make the communication success must meet the following two conditions:

1) Condition 1: The three period sum of phase-locked loop stability that PTX (or PRX) transmitted, amplifier enabled and phase-locked loop open loop must be 20us greater than the time of the PRX (or PTX) received phase-locked loop stabilization. This ensures that the time period during

which the PTX (or PRX) transmits data is within the time period during which the PRX (or PTX) receives the data, that is to say:

EX\_PA\_TIME + TX\_SETUP\_TIME + TRX\_TIME > RX\_SETUP\_TIME +20us

2) Condition 2: The four period sum of phase-locked loop stability that PRX transmitted ACK, amplifier enabled, phase-locked loop open loop and ACK transmitted must be 80us less than the two period sum of phase-locked loop stabilization that the PTX received and waiting for the ACK. This ensures that the time period during which the PRX replies ACK is within the time period during which the PTX waits for the ACK, that is to say:

$EX\_PA\_TIME + TX\_SETUP\_TIME + TRX\_TIME + SEND\_ACK\_TIME <$

RX\_SETUP\_TIME + RX\_ACK\_TIME - 80us

#### 6.7 One-To-Multi Communication at the Receiving End in Enhanced BURST

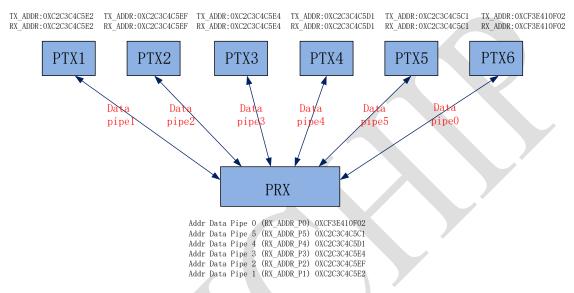

As a transmitter, the PAN2416AF chip can communicate with multiple receivers with different addresses for one-to-multi communications.

As a receiver, the PAN2416AF chip can receive the data from 6 channels of different addresses and the same frequency. Each data channel has its own address.

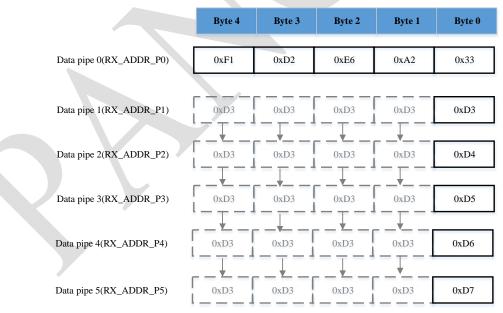

Those data channels which enabled are set by the register EN\_RXADDR. The address of each data channel is configured by register RX\_ADDR\_PX. In general, different data channels are not allowed to set the exactly same addresses. As shown below, an example of the configuration of multiple receive channel addresses is given in Figure 6-3.

Figure 6-3 Multi-channel address setting

It can be seen from Figure 6-3 that a total of 40 bits of 5 bytes of data channel 0 are configurable. The addresses of the data channel 1~5 are configured as 32 bit shared addresses (shared with data channel 1) and 8 bit respective addresses (minimum bytes).

The PAN2416AF chip can communicate with up to 6 different channels in receive mode, as shown

in Figure 6-4. Each data channel uses a different address and shares the same channel. All transmitters and receivers are set to enhanced mode.

After receiving valid data, PRX records the TX address of PTX and sends a response signal with this address as the destination address. When the PTX data channel 0 is used to receive a response signal, the RX address of the data channel 0 is equal to the TX address to ensure that the correct response signal is received. Figure 6-4 shows an example of how the PTX and PRX addresses are configured.

Figure 6-4 Example of Multichannel Data Transfer Response Address

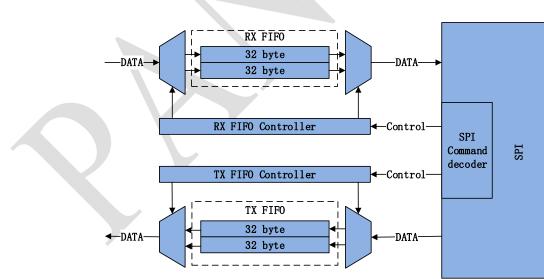

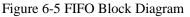

#### 6.8 DATA FIFO

PAN2416AF contains TX\_FIFO and RX\_FIFO. FIFO can be read and written through the SPI command. In transmit mode, TX\_FIFO is written with the W\_TX\_PAYLOAD and W\_TX\_PAY-LOAD\_NO\_ACK instructions. If a MAX\_RT interrupt is generated, the data in TX\_FIFO will not be cleared. In receive mode, the payload of RX\_FIFO is read with R\_RX\_PAYLOAD instruction. R\_RX\_PL\_WID instruction read the length of payload. The FIFO\_STATUS register indicates the

status of the FIFO.

#### 6.9 Interrupt Pin

The interrupt pin (IRQ) of PAN2416AF is triggered by a low level, the initial state of IRQ pin is high. When the TX\_DS, RX\_DR or MAX\_RT bit in the status register is set to 1, and the corresponding interrupt enable bit is set to 0, the IRQ pin interrupt is triggered. When the MCU writes '1' to the corresponding interrupt source, the interrupt is cleared. The interrupt trigger of IRQ pin can be masked or enabled by setting interrupt enable bit to 1 which IRQ pin interrupt is disabled.

# **7 SPI CONTROL INTERFACE**

The PAN2416AF is read and written to each register through the SPI control interface. The PAN2416AF is as a slave, and the data rate of the SPI interface generally depends on the interface speed of the MCU, its maximum data transmission rate is 4Mbps. In order to save power, the maximum transmission rate of SPI is 1Mbps in the sleep mode and standby mode-I.

The SPI interface is the standard SPI interface to see Table 7-1, which can be used to simulate the SPI interface with the universal I/O port of MCU. When the CSN pin is 0, the SPI interface waits for the execution instruction. A change from 1 to 0 of the CSN pin executes an instruction. After the CSN pin changes from 1 to 0, the content of the state register can be read through the MISO.

| PIN  | I/O direction | Function description            |

|------|---------------|---------------------------------|

| CSN  | input         | Chip select enable, low enabled |

| SCK  | input         | Clock                           |

| MOSI | input         | Serial input                    |

| MISO | output        | Serial output                   |

| Table 7-1 | SPI | Interface |

|-----------|-----|-----------|

|-----------|-----|-----------|

| Table 7-2 The Pin | Description | of the RF and | MCU Interface |

|-------------------|-------------|---------------|---------------|

|-------------------|-------------|---------------|---------------|

| Interface Function           | Interface | Interface  | Interface Name | Interface state |

|------------------------------|-----------|------------|----------------|-----------------|

|                              | Name (RF) | state (RF) | (MCU)          | (MCU)           |

| Mode chip select signal      | CE        | input      | RA7            | output          |

| SPI chip select signal       | CSN       | input      | RE2            | output          |

| SPI clock signal             | SCK       | input      | RE1            | output          |

| SPI data master out slave in | MOSI      | input      | RA5            | output          |

| SPI data master in slave out | MISO      | output     | RA4            | input           |

| Interrupt Signal             | IRQ       | output     | RA3            | input           |

Note: The interface status of the RF part in Table 7-2 are the default status and can not be changed. The interface status of MCU part need to be configured by the software to the table above, the chip can work properly.

#### 7.1 SPI Instruction Format

<Command word: MS Bit to LS Bit (one byte)>

<Data bytes: LS Byte to MS Byte, MS Bit in each byte first>

| Command    | Command word (binary) | Data bytes         Operation |                               |

|------------|-----------------------|------------------------------|-------------------------------|

| R REGISTER | 000A AAAA             | 1 to 5                       | Read status register          |

| K_KEGISTEK | 000A AAAA             | LS Byte first                | AAAAA = 5bit register address |

| W_REGISTER | 001A AAAA             | 1 to 5                       | Write status register         |

#### Table 7-3 SPI commands

|                       |           | LS Byte first | AAAAA = 5bit register address                         |  |  |

|-----------------------|-----------|---------------|-------------------------------------------------------|--|--|

|                       |           |               | Only work in power down and standby mode-I            |  |  |

|                       |           | 1 to 32/64    | Read the receiving data, read usually starts from 0   |  |  |

| R_RX_PAYLOAD          | 0110 0001 | LS Byte first | bytes, and the data will be deleted from RX FIFO      |  |  |

|                       |           | Lo byte mst   | after reading, work in receive mode.                  |  |  |

| W_TX_PAYLOAD          | 1010 0000 | 1 to 32/64    | Write transmit mode, the write operation is usually   |  |  |

|                       | 1010 0000 | LS Byte first | started from 0 bytes.                                 |  |  |

| FLUSH_TX              | 1110 0001 | 0             | Clear TX FIFO                                         |  |  |

| FLUSH_RX              | 1110 0010 | 0             | Clear RX FIFO                                         |  |  |

|                       |           |               | Used at the PTX side, the data sent in the last frame |  |  |

|                       |           |               | is used again and sent. This command is available     |  |  |

| REUSE_TX_PL           | 1110 0011 | 0             | immediately after sending data and executing the      |  |  |

|                       |           |               | FLUSH_TX. This command can not be used dur-           |  |  |

|                       |           |               | ing data transmission.                                |  |  |

|                       |           |               | With this command followed by data 0x73, the fol-     |  |  |

| ACTIVATE              |           |               | lowing functions are activated:                       |  |  |

|                       |           |               | • R RX PL WID                                         |  |  |

|                       |           |               | • W TX PAYLOAD NOACK                                  |  |  |

|                       | 0101 0000 | 1             | • W ACK PAYLOAD                                       |  |  |

|                       |           |               | This command is only executed in sleep and            |  |  |

|                       |           |               | standby modes.                                        |  |  |

| DEACTIVATE            |           |               | With this command followed by data 0x8C, the          |  |  |

|                       |           |               | above function will be disabled.                      |  |  |

|                       |           |               | Read the top RX-payload data width of the RX          |  |  |

| R_RX_PL_WID           | 0110 0000 | 0             | FIFO.                                                 |  |  |

|                       |           |               | Rx mode is available.                                 |  |  |

|                       |           |               | Write Payload to be transmitted together with ACK     |  |  |

|                       |           |               | packet on PIPE PPP. (PPP valid in the range from      |  |  |

| W_ACK_PAY-            | 1010 1PPP | 1 to 32/64    | 000 to 101). Up to 2 ACK packets can be set. The      |  |  |

| LOAD                  |           | LS Byte first | data of the same PIPE will be sent following the      |  |  |

|                       |           |               | principle of first-in first-out. Write usually starts |  |  |

|                       |           |               | from 0 bytes                                          |  |  |

|                       |           |               | Write transmit data, usually start from 0 bytes. Ex-  |  |  |

| W_TX_PAY-             | 1011 0000 | 1 to 32/64    | ecution in TX mode, using this command to send        |  |  |

| LOAD_NOACK            |           | LS Byte first | data does not treat as automatic response.            |  |  |

|                       |           |               | The SPI command sets the inside logic of the CE       |  |  |

| CE_FSPI_ON            | 1111 1101 | 1             | to 1, followed by data 0x00 after this command.       |  |  |

|                       |           |               | The SPI command sets the inside logic of the CE       |  |  |

| CE_FSPI_OFF           | 1111 1100 | 1             | to 0, followed by data 0x00 after this command.       |  |  |

| RST_FSPI_HOLD         |           |               | Use this command followed by data 0x5A, enter         |  |  |

|                       |           |               | the reset state and hold.                             |  |  |

|                       | 0101 0011 | 1             | Use this command followed by data 0xA5, release       |  |  |

| RST_FSPI_RELS         |           |               | the reset state and start to work properly.           |  |  |

| ···· · _· ··· · _···· | l         |               | the reper state and start to work property.           |  |  |

| NOP | 1111 1111 | 0 | No operation. |

|-----|-----------|---|---------------|

|     |           |   |               |

The R\_REGISTER and W\_REGISTER registers may operate on single-byte or multi-byte registers. The first byte to be read / written when accessing a multi-byte register is the high bit of the lowest byte. Multi-byte registers can write part of the byte only, the high byte without written will keep the original content unchanged. For example: The lowest byte of the RX\_ADDR\_P0 register can be changed by writing a byte to the register RX\_ADDR\_P0.

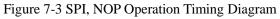

#### 7.2 Timing Sequence

Table 7-4 SPI Operation Reference time

| Symbol | Parameters            | Min | Max | Units |

|--------|-----------------------|-----|-----|-------|

| Tdc    | Data set-up time      | 15  | -   | ns    |

| Tdh    | Data hold-up time     | 2   | -   | ns    |

| Tcsd   | CSN signal valid time | -   | 40  | ns    |

| Tcd   | SCK signal valid time         | -  | 51  | ns  |

|-------|-------------------------------|----|-----|-----|

| Tcl   | SCK signal low level time     | 38 | -   | ns  |

| Tch   | SCK signal high level time    | 38 | -   | ns  |

| Fsck  | SCK signal frequency          | -  | 8   | MHz |

| Tr,Tf | SCK signal rise and fall time | -  | 110 | ns  |

| Тсс   | CSN signal setup time         | 2  | -   | ns  |

| Tcch  | CSN signal holdup time        | 2  | -   | ns  |

| Tcwh  | CSN invalid time              | 49 | -   | ns  |

| Tcdz  | CSN signal high impedance     | -  | 40  | ns  |

Note: The parameters of Table 7-4 can be adjusted according to the selected MCU.

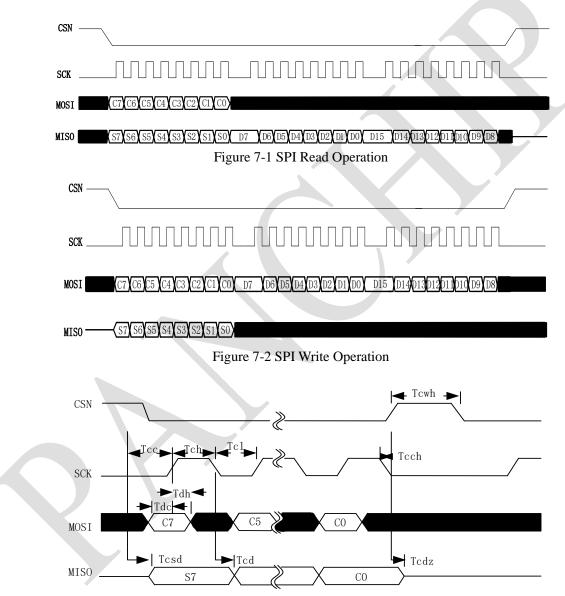

Figure 7-1 through Figure 7-3 and Table 7-4 show the SPI operation and timing. The following symbols are used in the figure:

Ci-SPI instruction bit

Si-Status register bit

Di-Data bit (Remarks: From low byte to high byte, high in the front at each byte )

Among: i=1, 2, 3.....n.

# **8 CONTROL REGISTER**

You can configure and control the PAN2416AF by SPI reading and writing the registers in Table 8-1. Registers whose address with symbol \* need to be modified when being used.

| Address | Register    | Bit | Reset value | type | Description                                        |

|---------|-------------|-----|-------------|------|----------------------------------------------------|

| (hex)   |             |     |             |      |                                                    |

|         | CONFIG      | -   | -           | -    | Working register                                   |

|         |             |     |             |      | Enter STB3 mode                                    |

|         |             | 7   | 0           | R/W  | (Precondition PWR_UP=1)                            |

|         |             |     |             |      | 1: enter STB3                                      |

|         | EN_PM       |     |             |      | 0: enter STB1                                      |

|         |             |     |             |      | (In the STB3 mode, it is necessary to wait for     |

|         |             |     |             |      | more than 50uS to jump to other working states)    |

|         |             |     | 0           |      | Interrupt enable bit of receiving data successful  |

|         | MACK DY DD  | 6   |             | R/W  | 1: Interrupts are not reflected on the IRQ pin     |

|         | MASK_RX_DR  |     |             |      | 0: The RX_DR interrupt is reflected on the IRQ     |

|         |             |     |             |      | pin                                                |

|         |             | 5   | 0           | R/W  | Interrupt enable bit of transmitting Data Success- |

|         |             |     |             |      | ful                                                |

|         | MASK_TX_DS  |     |             |      | 1: Interrupts are not reflected on the IRQ pin     |

|         |             |     |             |      | 0: The TX_DR interrupt is reflected on the IRQ     |

| 00*     |             |     |             |      | pin                                                |

|         |             | 4   | 0           | R/W  | Interrupt enable bit of sending fail and reaching  |

|         | MASK_MAX_RT |     |             |      | maximum transmit times                             |

|         |             |     |             |      | 1: Interrupts are not reflected on the IRQ pin     |

|         |             |     |             |      | 0: The MAX_RT interrupt is reflected on the IRQ    |

|         |             |     |             |      | pin                                                |

|         | EN_CRC      | 3   | 1           | R/W  | CRC enable bit                                     |

|         |             |     |             |      | 1: CRC enabled, 2 byte                             |

|         |             |     |             |      | 0: CRC not enabled, and No CRC verification        |

|         | N/A         | 2   | 0           | R/W  | Saved, need to be set to 1                         |

|         | PWR_UP      | 1   | 0           | R/W  | Chip enable bit                                    |

|         |             |     |             |      | 1: POWER_UP                                        |

|         |             |     |             |      | 0: POWER_DOWN                                      |

|         | PRIM_RX     | 0   | 0           | R/W  | RX/TX control bit                                  |

|         |             |     |             |      | 1: PRX                                             |

|         |             |     |             |      | 0: PTX                                             |

|         | EN_AA       |     |             |      | The automatic response enable of the receiving     |

| 01      | Enhanced    | -   | -           | -    | channel(When EN_AA of receiver is not 0X00, it     |

|         | Burst       |     |             |      | is enhanced mode)                                  |

Table 8-1 Control Register

|     | Reserved   | 7:6 | 00      | R/W | Only 00 allowed                                    |

|-----|------------|-----|---------|-----|----------------------------------------------------|

|     | ENAA_P5    | 5   | 0       | R/W | Enable auto acknowledgement data pipe 5            |

|     | ENAA_P4    | 4   | 0       | R/W | Enable auto acknowledgement data pipe 4            |

|     | ENAA_P3    | 3   | 0       | R/W | Enable auto acknowledgement data pipe 3            |

|     | ENAA_P2    | 2   | 0       | R/W | Enable auto acknowledgement data pipe 2            |

|     | ENAA_P1    | 1   | 0       | R/W | Enable auto acknowledgement data pipe 1            |

|     | ENAA_P0    | 0   | 1       | R/W | Enable auto acknowledgement data pipe 0            |

|     | EN_RXADDR  | -   | -       | -   | Enable of the receiving channel                    |

|     | Reserved   | 7:6 | 00      | R/W | Only 00 allowed                                    |

|     | ERX_P5     | 5   | 0       | R/W | Data pipe5 enabled                                 |

| 02  | ERX_P4     | 4   | 0       | R/W | Data pipe4 enabled                                 |

| 02  | ERX_P3     | 3   | 0       | R/W | Data pipe3 enabled                                 |

|     | ERX_P2     | 2   | 0       | R/W | Data pipe2 enabled                                 |

|     | ERX_P1     | 1   | 0       | R/W | Data pipe1 enabled                                 |

|     | ERX_P0     | 0   | 1       | R/W | Data pipe0 enabled                                 |

|     | SETUP_AW   | -   | -       |     | Address width setting                              |

|     | Reserved   | 7:2 | 000000  | R/W | Only 000000 allowed                                |

|     |            |     |         |     | RX/TX address width                                |

|     | AW         | 1:0 | n       |     | 00: invalid                                        |

| 03  |            |     |         | R/W | 01: 3 bytes                                        |

|     |            |     |         |     | 10: 4 bytes                                        |

|     |            |     |         |     | 11: 5 bytes                                        |

|     |            |     |         |     | If the address width is set below 5 bytes, the ad- |

|     |            |     |         |     | dress uses the LS byte                             |

|     | SETUP_RETR | -   | -       | -   | Automatic transmission setting                     |

|     |            |     |         |     | Automatic transmission delay                       |

|     | ARD        | 7:4 | 0000    | R/W | 0000: 250µs                                        |

|     |            |     |         |     | 0001: 500µs                                        |

|     |            |     |         |     | 0010: 750µs                                        |

|     |            |     |         |     |                                                    |

|     |            |     |         |     | 1111: 4000µs                                       |

| 04  |            |     |         |     | Automatic setting for the number of transmission   |

|     | ARC        | 3:0 | 0011    | R/W | 0000: normal mode                                  |

|     |            |     |         |     | 0001~1111: enhanced mode                           |

|     |            |     |         |     | 0001: enhanced 1 transmission                      |

|     |            |     |         |     | 0002: enhanced 2 transmission                      |

|     |            |     |         |     |                                                    |

|     |            |     |         |     | 1111: enhanced 15 transmission                     |

| 05  | RF_CH      | -   | -       | -   | Communication channel setting                      |

|     | Reserved   | 7   | 0       | R/W | Only 0 allowed                                     |

|     |            |     | 1001110 | R/W | The use channel is set as                          |

|     | RF_CH      | 6:0 | 1001110 |     | Channel=RF_CH + 2400                               |

| 06* | RF_SETUP   | -   | -       | -   | Communication parameters configuration             |

| L   | 1          |     | 1       | 1   | - 0                                                |

|    | RF_DR      | 7:6 | 00  | R/W | Data rate<br>01: 2Mbps<br>00: 1Mbps<br>11: 250kbps<br>10: saved                                                                                                                                                                                                                                           |

|----|------------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | PA_GC      | 5:3 | 111 | R/W | The output amplitude of PA's driver level, the transmitted power can be adjusted.<br>111: large amplitude<br><br>000: small amplitude                                                                                                                                                                     |

|    | PA_PWR     | 2:0 | 111 | R/W | The power selection of PA's output level, the transmitted power can be adjusted.<br>111: large output power<br><br>000: small output power                                                                                                                                                                |

|    | STATUS     | -   | -   | -   | State register                                                                                                                                                                                                                                                                                            |

|    | Reserved   | 7   | 0   | R/W | Only 0 allowed                                                                                                                                                                                                                                                                                            |

| 07 | RX_DR      | 6   | 0   | R/W | The receiving data interrupt bit of RX FIFO, an interrupt is generated when new data is received and reaches the RX FIFO.<br>Write 1 to clear bit.                                                                                                                                                        |

|    | TX_DS      | 5   | 0   | R/W | The sending data interrupt bit of TX FIFO.<br>Without automatic retransmission mode, an inter-<br>rupt is generated after data transmission com-<br>pletes.<br>With automatic retransmission mode, this bit is<br>set high only after the sender has received the<br>ACK signal.<br>Write 1 to clear bit. |

|    | MAX_RT     | 4   | 0   | R/W | Maximum number of TX retransmits interrupt<br>write 1 to clear bit. If MAX_RT is asserted it must<br>be cleared to enable further communication.                                                                                                                                                          |

|    | RX_P_NO    | 3:1 | 111 | R   | Read pipe's number from RX_FIFO<br>000-101: pipe number<br>110: Not used<br>111: RX_FIFO null                                                                                                                                                                                                             |

|    | TX_FULL    | 0   | 0   | R   | TX FIFO full mark<br>1: TX FIFO is full<br>0: TX FIFO is not full and is available                                                                                                                                                                                                                        |

|    | OBSERVE_TX | -   | -   | -   | Transmission status register                                                                                                                                                                                                                                                                              |

| 08 | PLOS_CNT   | 7:4 | 0   | R   | Packet loss counter<br>The counter will stop counting when it reaches<br>the maximum value of 15.                                                                                                                                                                                                         |

|     |            |      |                  |     | This counter is reset when RF_CH is written.        |

|-----|------------|------|------------------|-----|-----------------------------------------------------|

|     |            |      |                  |     | When this value is not reset, communication can     |

|     |            |      |                  |     | continue.                                           |

|     |            |      |                  |     | The transmission times counter of automatic re-     |

|     |            |      |                  |     | transmission.                                       |

|     |            |      |                  |     | Transmit once more, then ARC_CNT adds one.          |

|     | ARC_CNT    | 3:0  | 0                | R   | When the ARC_CNT reaches the ARC limit, it is       |

|     | _          |      |                  |     | regarded as a packet loss and a PLOS_CNT plus       |

|     |            |      |                  |     | one. The counter is reset when the new data is      |

|     |            |      |                  |     | written to TX FIFO.                                 |

|     |            |      |                  |     | Data read register (The premise is                  |